Consulte las especificaciones para obtener detalles del producto.

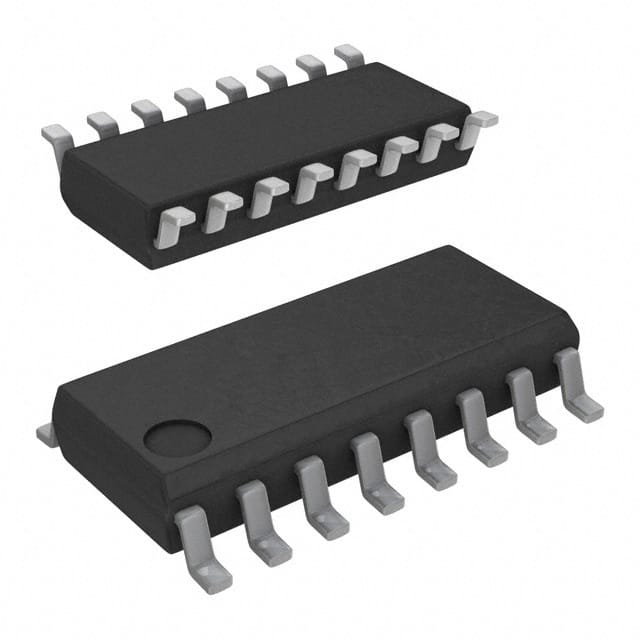

CD4027BMG4

Product Overview

- Category: Integrated Circuit (IC)

- Use: Flip-Flop

- Characteristics: Dual J-K Master-Slave Flip-Flop, CMOS Technology

- Package: SOIC (Small Outline Integrated Circuit)

- Essence: Sequential Logic Device

- Packaging/Quantity: Tape and Reel, 2500 pieces per reel

Specifications

- Supply Voltage Range: 3V to 18V

- High-Level Input Voltage: 2V

- Low-Level Input Voltage: 0.8V

- High-Level Output Voltage: VDD - 0.5V

- Low-Level Output Voltage: 0.5V

- Maximum Operating Frequency: 25MHz

- Propagation Delay Time: 60ns

- Operating Temperature Range: -55°C to +125°C

Pin Configuration

The CD4027BMG4 has a total of 16 pins. The pin configuration is as follows:

- J1 - J input for the first flip-flop

- K1 - K input for the first flip-flop

- CP1 - Clock input for the first flip-flop

- Q1 - Output of the first flip-flop

- Q̅1 - Complementary output of the first flip-flop

- GND - Ground

- Q̅2 - Complementary output of the second flip-flop

- Q2 - Output of the second flip-flop

- CP2 - Clock input for the second flip-flop

- K2 - K input for the second flip-flop

- J2 - J input for the second flip-flop

- VDD - Positive power supply

- NC - No connection

- NC - No connection

- NC - No connection

- NC - No connection

Functional Features

- Dual J-K Master-Slave Flip-Flop: The CD4027BMG4 consists of two independent J-K flip-flops, allowing for the storage and transfer of binary data.

- CMOS Technology: The use of CMOS technology in this IC provides low power consumption and high noise immunity.

- Asynchronous Reset: The flip-flops can be reset asynchronously using the reset pin (CP1 and CP2).

- Edge-Triggered Clocking: The flip-flops are triggered by the rising edge of the clock signal.

Advantages and Disadvantages

Advantages: - Low power consumption due to CMOS technology - High noise immunity - Compact SOIC package - Asynchronous reset capability

Disadvantages: - Limited maximum operating frequency compared to some other flip-flop ICs - Not suitable for high-speed applications

Working Principles

The CD4027BMG4 is a sequential logic device that operates based on the principles of flip-flops. It uses J-K flip-flops to store and transfer binary data. The flip-flops are triggered by the rising edge of the clock signal, and the stored data can be reset asynchronously using the reset pins. The CMOS technology used in this IC ensures low power consumption and high noise immunity.

Detailed Application Field Plans

The CD4027BMG4 can be used in various applications that require sequential logic, such as:

- Counters: The flip-flops can be connected in a cascaded manner to create binary counters for applications like frequency division, timekeeping, or event counting.

- Shift Registers: By connecting multiple flip-flops, the IC can be used to implement shift registers for serial data transmission or storage.

- Control Circuits: The flip-flops can be utilized in control circuits to store and transfer control signals for various systems.

Detailed and Complete Alternative Models

Some alternative models to the CD4027BMG4 include:

- CD4013BMG4: Dual D-Type Flip-Flop

- CD4042BMG4: Quad Clocked D Latch

- CD4073BMG4: Triple 3-Input AND Gate

These alternative models offer different functionalities and can be chosen based on specific application requirements.

Word count: 399 words

Enumere 10 preguntas y respuestas comunes relacionadas con la aplicación de CD4027BMG4 en soluciones técnicas

Sure! Here are 10 common questions and answers related to the application of CD4027BMG4 in technical solutions:

Q: What is CD4027BMG4? A: CD4027BMG4 is a dual J-K flip-flop integrated circuit (IC) that can be used in various digital logic applications.

Q: What is the purpose of CD4027BMG4? A: CD4027BMG4 is primarily used for storing and manipulating binary data in electronic circuits.

Q: What are the key features of CD4027BMG4? A: Some key features include low power consumption, wide operating voltage range, and high noise immunity.

Q: How does CD4027BMG4 work? A: CD4027BMG4 consists of two independent J-K flip-flops, which can be triggered by clock signals to store or change binary data.

Q: What are the typical applications of CD4027BMG4? A: CD4027BMG4 is commonly used in counters, frequency dividers, shift registers, and other digital systems requiring sequential logic.

Q: What is the maximum operating frequency of CD4027BMG4? A: The maximum operating frequency of CD4027BMG4 is typically around 25 MHz.

Q: Can CD4027BMG4 handle both positive and negative edge-triggered inputs? A: No, CD4027BMG4 is only capable of positive edge-triggered operation.

Q: What is the power supply voltage range for CD4027BMG4? A: CD4027BMG4 can operate with a power supply voltage ranging from 3V to 18V.

Q: Does CD4027BMG4 have any built-in protection features? A: Yes, CD4027BMG4 has built-in diode clamps to protect against static discharge and voltage spikes.

Q: Is CD4027BMG4 available in different package types? A: Yes, CD4027BMG4 is available in various package options, including DIP (Dual In-line Package) and SOIC (Small Outline Integrated Circuit).

Please note that the answers provided here are general and may vary depending on the specific datasheet and manufacturer's specifications for CD4027BMG4.